86KB7Z

在电子工程领域,FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,能够根据用户需求配置成各种数字电路。在本话题中,我们关注的是如何利用FPGA生成高斯白噪声。高斯白噪声是一种随机信号,其功率谱密度在整个频率范围内均匀分布,且每个样本值遵循正态分布,即高斯分布。

生成高斯白噪声有多种方法,常见的包括线性反馈移位寄存器(LFSR)、伪随机数生成器(PRNG)以及滤波器等。在FPGA中,由于其并行处理能力,可以高效地实现这些算法。

1. Verilog语言:Verilog是硬件描述语言之一,用于编写FPGA的设计代码。在生成高斯白噪声的过程中,我们可以用Verilog设计一个PRNG,然后通过合适的滤波器(如IIR或FIR滤波器)将生成的伪随机序列转换为具有高斯分布的噪声。Verilog代码通常包含以下几个部分:

– 初始化模块:设定初始种子,确保每次启动时生成的序列不同。

– PRNG模块:实现线性同余法或其他随机数生成算法。

– 滤波器模块:设计滤波器结构,如巴特沃兹滤波器,以调整噪声的频谱特性。

– 输出模块:提供噪声信号输出接口。

2. 高斯化过程:伪随机数序列通常遵循均匀分布,需要经过某种转换才能变为高斯分布。一种常用的方法是Box-Muller变换,它将两个独立的均匀分布随机数转换为一对独立的标准正态分布(即均值为0,方差为1的高斯分布)随机数。

3. FPGA实现优势:FPGA的并行处理能力使得它可以同时处理多个计算任务,从而提高噪声生成的速度。此外,FPGA设计的灵活性允许我们针对特定应用调整噪声参数,例如噪声的带宽、功率和信噪比。

4. 应用场景:高斯白噪声在通信系统中常用于模拟信道干扰,测试接收机的性能;在信号处理中作为加性噪声模型;在雷达和声纳系统中用于模拟环境杂波;在音频和视频编码中进行信道仿真等。

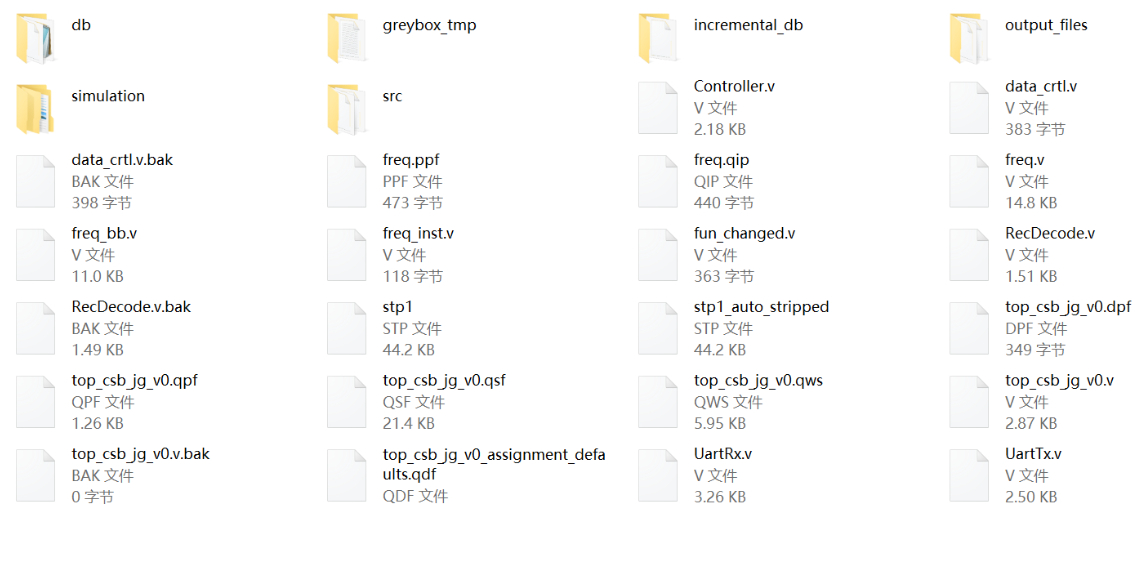

使用FPGA生成高斯白噪声是通过Verilog编程实现的,涉及到的关键技术包括PRNG的Verilog实现、滤波器设计和高斯化算法。这样的设计可以满足各种实时性和性能要求,广泛应用于各种信号处理和通信系统。在实际项目中,`GWN`可能是一个包含了上述设计元素的Verilog源代码文件或者相关的测试波形文件。11

资源声明(购买视为同意此声明): 1.在网站平台的任何操作视为已阅读和同意网站底部的注册协议及免责声明,本站资源已是超低价,且不提供技术支持 2.部分网络用户分享网盘地址有可能会失效,如发生失效情况请发邮件给客服code711cn#qq.com (把#换成@)会进行补发 3.本站站内提供的所有可下载资源(软件等等)本站保证未做任何负面改动;但本网站不能保证资源的准确性、安全性和完整性,用户下载后自行斟酌,我们以交流学习为目的,并不是所有的源码都不是100%无错或无bug;需要您有一定的基础能够看懂代码,能够自行调试修改代码并解决报错。同时本站用户必须明白,源码便利店对提供下载的软件等不拥有任何权利,其版权归该资源的合法拥有者所有。 4.本站所有资源仅用于学习及研究使用,请必须在24小时内删除所下载资源,切勿用于商业用途,否则由此引发的法律纠纷及连带责任本站和发布者概不承担 5.因资源可复制性,一旦购买均不退款,充值余额也不退款

![ISE开发环境使用指南[FPGA开发实用教程].pdf](https://code711.cn/wp-content/uploads/2024/08/20240815142919-66be10bf6df9c.jpg)