1.92MBRAR

在电子设计领域,VHDL(Very High-Speed Integrated Circuit Hardware Description Language)是一种广泛使用的硬件描述语言,用于描述数字系统的逻辑功能和行为。本项目“dd.rar_抢答器_抢答器 VHDL”是一个基于VHDL的抢答器设计实例,旨在帮助学习者理解和掌握如何用VHDL实现一个简单的抢答系统。

抢答器的设计通常包含以下几个关键部分:

1. **输入信号**:抢答器通常有多个输入,对应于每个参赛者的抢答按钮。在VHDL中,这些输入可能被定义为二进制位,例如4个参赛者则需要4个输入位,每个代表一个参赛者。

2. **计时逻辑**:为了公平起见,抢答器通常有一个开始信号和一个计时窗口。开始信号激活后,参赛者才能按下抢答按钮,而计时窗口则限制了抢答的有效时间。

3. **状态机**:抢答器的逻辑处理通常通过一个状态机来实现,它管理抢答过程中的各个阶段,如等待开始、抢答中、显示获胜者等。

4. **输出信号**:当有参赛者按下按钮并在有效时间内,抢答器会输出获胜者的编号。此外,可能还有其他的辅助输出,如显示抢答成功的LED灯或声音提示。

5. **同步与异步逻辑**:VHDL设计中,需要考虑同步和异步信号的处理,以确保在高速数字系统中的正确工作。

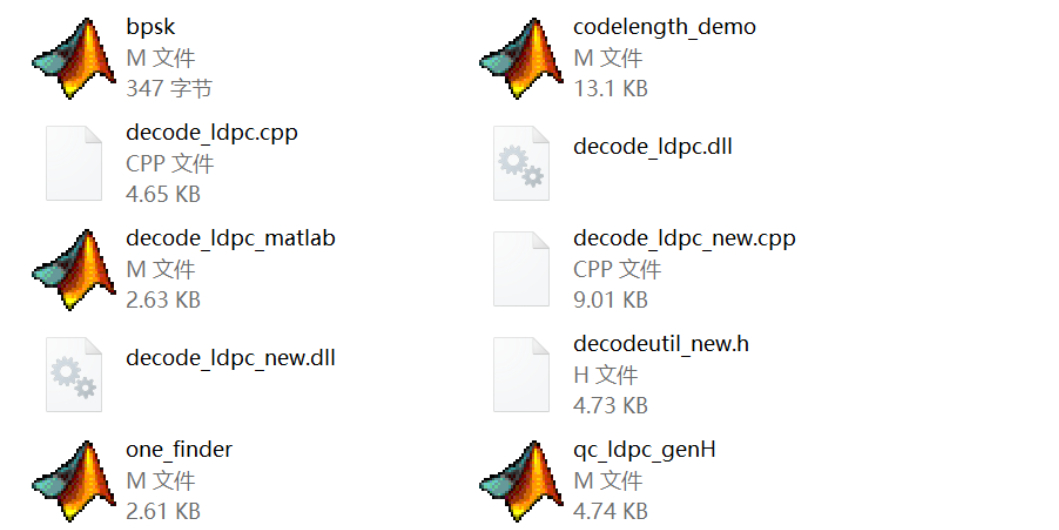

在实验5_抢答器设计实验程序中,可能会包含以下文件:

– **设计文件**:这个文件可能包含VHDL代码,定义了抢答器的结构和行为,包括输入、输出、状态机和逻辑运算。

– **仿真文件**:用于验证设计是否按预期工作的仿真脚本,可能使用了像ModelSim或GHDL这样的工具。

– **测试平台**:为了测试设计,可能有一个测试平台文件,它提供了一组输入信号,并检查输出是否符合预期。

通过这个实验,学习者可以了解到如何使用VHDL描述数字逻辑,如何编写状态机,以及如何进行硬件级别的设计验证。这不仅有助于理解数字系统的工作原理,也为将来更复杂的FPGA或ASIC设计打下基础。在实际应用中,这样的抢答器设计可能还需要考虑到电源管理、抗干扰措施以及与其他系统(如显示设备或控制单元)的接口设计。通过VHDL,所有这些都可以被精确地描述和实现。

资源声明(购买视为同意此声明): 1.在网站平台的任何操作视为已阅读和同意网站底部的注册协议及免责声明,本站资源已是超低价,且不提供技术支持 2.部分网络用户分享网盘地址有可能会失效,如发生失效情况请发邮件给客服code711cn#qq.com (把#换成@)会进行补发 3.本站站内提供的所有可下载资源(软件等等)本站保证未做任何负面改动;但本网站不能保证资源的准确性、安全性和完整性,用户下载后自行斟酌,我们以交流学习为目的,并不是所有的源码都不是100%无错或无bug;需要您有一定的基础能够看懂代码,能够自行调试修改代码并解决报错。同时本站用户必须明白,源码便利店对提供下载的软件等不拥有任何权利,其版权归该资源的合法拥有者所有。 4.本站所有资源仅用于学习及研究使用,请必须在24小时内删除所下载资源,切勿用于商业用途,否则由此引发的法律纠纷及连带责任本站和发布者概不承担 5.因资源可复制性,一旦购买均不退款,充值余额也不退款